### Using Cutting-Edge Tools to Test Firmware for Uninterruptible Power Supplies

**HIL & Real time Power Electronics Simulation**

Jean-Louis Schricke - MESULOG

# **SOCOMEC** Activities

### **Critical Power**

Ensuring the availability of high-quality power for critical applications

### **Energy Efficiency**

Improving the energy performance of buildings and installations

### **Power Control & Safety**

Managing power and protecting people, equipment and installations

Enabling available, safe and efficient energy

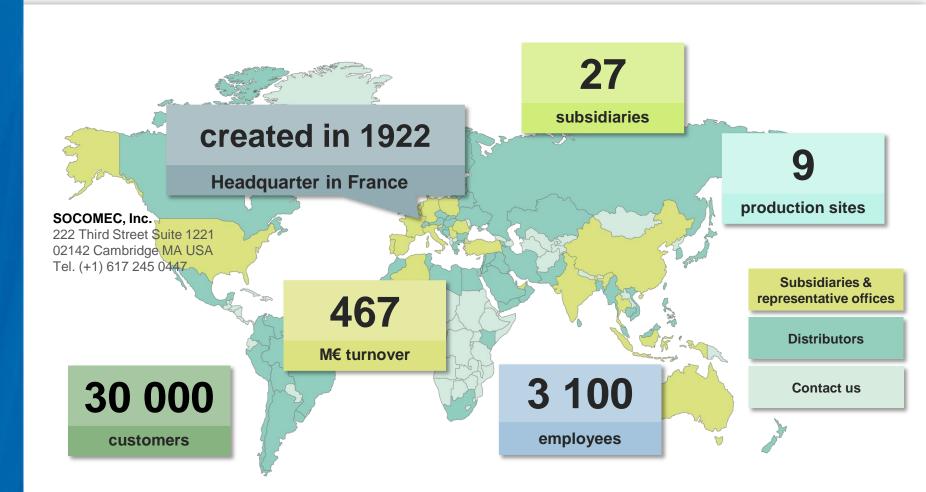

# **SOCOMEC** Figures

3

## Critical Power Specialist positioning

4

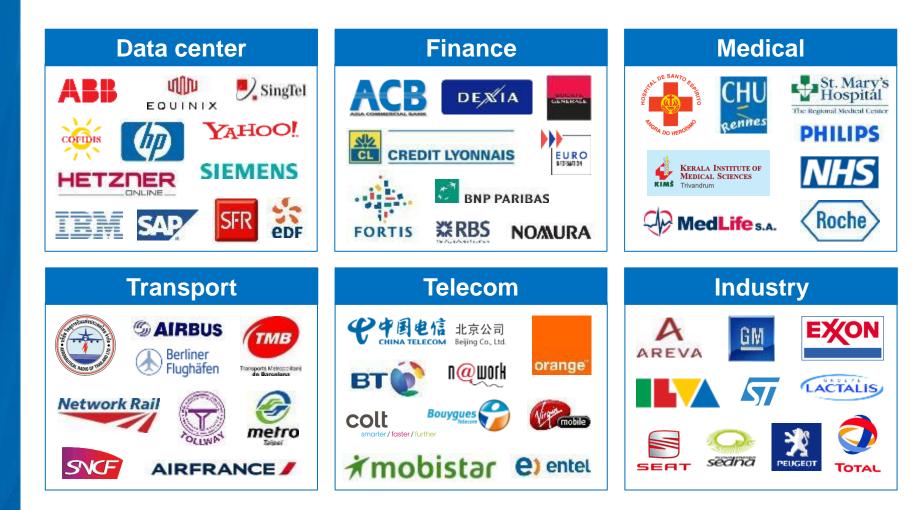

# Critical Power Customer confidence

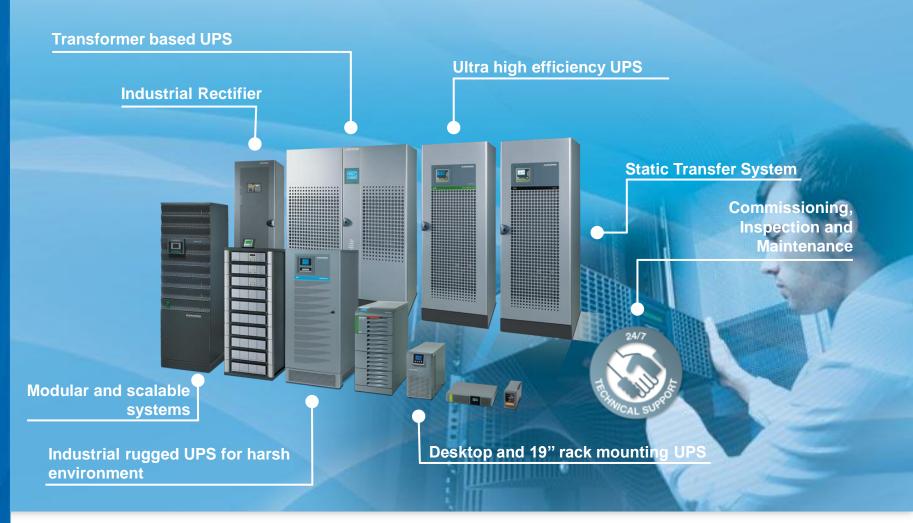

### Critical Power A wide range of solutions...

## Critical Power Continuous innovation

**1968** 1<sup>st</sup> UPS

**1987** 1<sup>st</sup> Static Transfer System (STS)

**1988** Transistor technology (600 kVA)

**1989** IGBT & microprocessor **1990** Distributed parallel architecture

**1994** Transformerless technology

**1996** IGBT up to 800 kVA

**1998** Digital Signal Processor (DSP) **2001** 1<sup>st</sup> modular UPS

2003 IGBT rectifiers up to 200 kVA

2004 Expert Battery System (EBS)

2006 Flywheel UPS

2008 High efficiency UPS **2010** Green Power

**2012** High power 3L technology

**2014** "Forever Young" design for modular UPS

2015

Rack-mounted modular UPS

Innovative Battery reinjection test

Real hot-scalable UPS system up to 1.2 MW

7

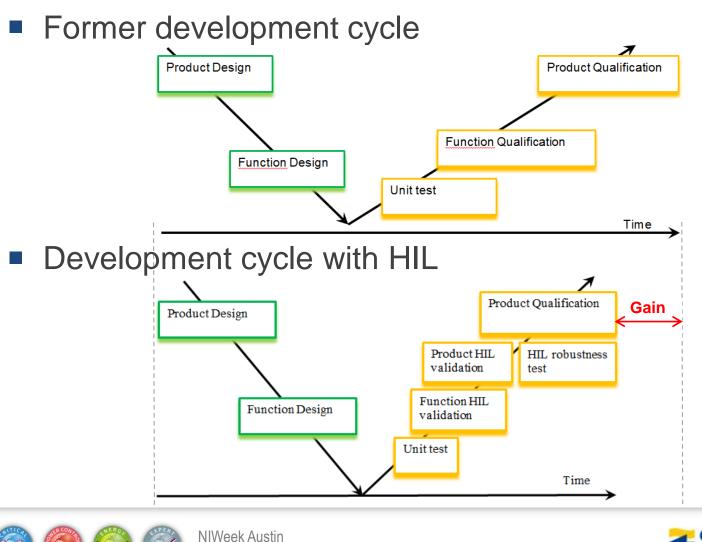

- 2016: why an HIL simulator ?

- Shorten the development time

- Test new added functionalities

- Do not blow costly (and rare) prototypes

- Reproduce harsh environment variables (grid dips, voltage distortion, frequency variations, etc.)

- Realize full featured non regression test

### → Continue improving product quality

# Critical Power Continuous improvement

- Development process :

- Specification reviews

- Design reviews

- Coding reviews

- Unit test

### • Product qualification

- done by experts on specific items

- Field

- Problems seen on the field (environment)

Many feedbacks

Few feedbacks

# Critical Power Continuous improvement

- Development process :

- Specification reviews

- Design reviews

- Coding reviews

- Unit test

- Testing modifications with HIL

- Regression test done with HIL

- Robustness test done with HIL (voltage / frequency limits / sensor failures, etc.)

- Product qualification

- done by experts on specific items

- Field

- Reproduce problems seen on the field (waveforms, environment)

Many feedbacks

August 2016

# Critical Power Continuous improvement

August 2016

- Physical characteristics

- Switching frequency above 10 kHz

- All signals of a unit shall be simulated

- Accurate simulated signals in order to use standard firmware

- For a unit : 150 environment variables

- More than 50 electronic components (diodes, IGBTs, SCRs)

- Real time constraints above 100 kHz (10 µs)

- More than 30 analog signals

- More than 40 PWM signals

- Real time constraints about 1 kHz (1 ms)

- Temperature sensors

- Auxiliary switches

- Digital outputs

- User-friendly HIL simulation

- No specific modelling knowledge

- Change the simulated device in a short time

- Use standard device schematics like PSIM

- Avoid any FPGA compilation

- Use standard test tools

- Integrated solution

- One hardware platform for all functionalities

- One supplier for test software

- What has to be simulated ?

- Power electronics (IGBTs, SCRs)

- 3 level power bridges from 3 to 300 kW

- Power components

- resistors, inductors, capacitors, transformer

- DC energy storage

- Batteries (lead acid, nickel cadmium, lithium-ion)

- Lithium-ion capacitors

- Load

- Motors

- Non-linear loads

- AC generators

- Grid or gensets (voltage and frequency variation)

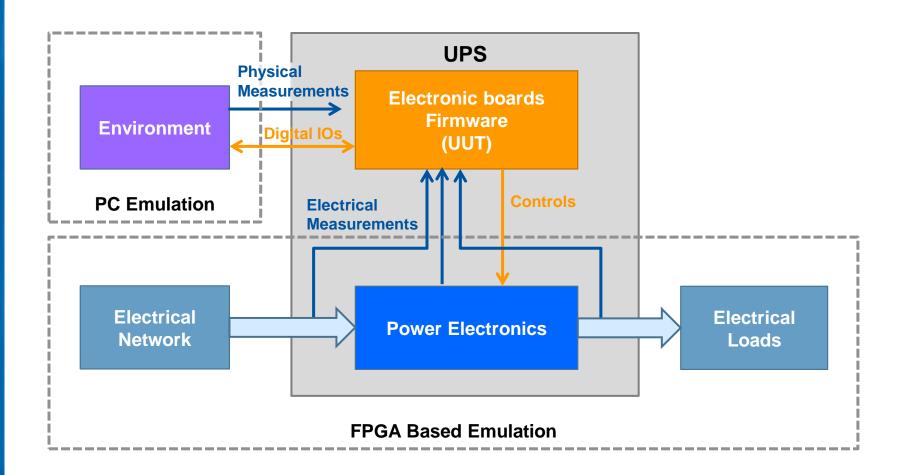

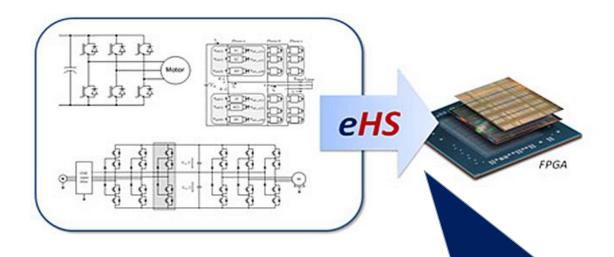

eHS is a revolutionary floating-point solver for *physical real-time simulation of an electric circuit on FPGA.*

No Mathematical Modeling No FPGA expertise No VHDL programming

Opal-RT eHSx64 solver

|               | eHSx64    |  |

|---------------|-----------|--|

| Inputs        | 48        |  |

| Outputs       | 32        |  |

| Switches      | > 64      |  |

| L-C           | 150       |  |

| R             | Unlimited |  |

| NPC time step | ~ 200ns   |  |

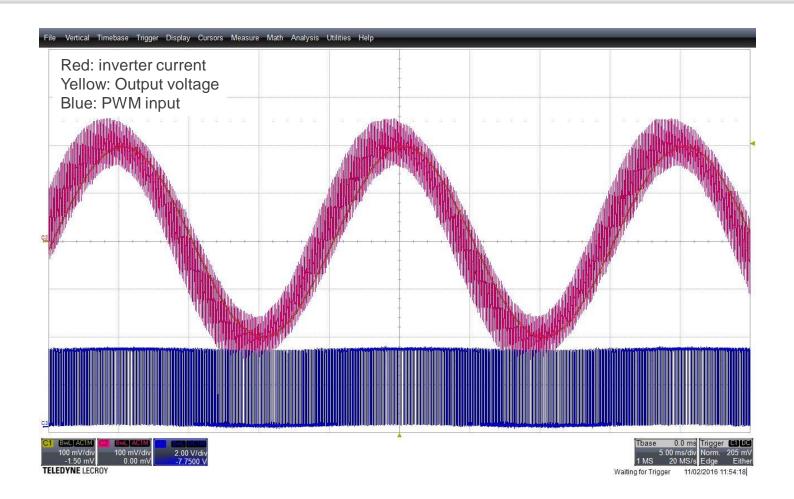

- < 1 µs computing cycle

- Overall delay (PWM input to analog output about 4 µs) thanks to the high data transfer rate of the PXIe bus

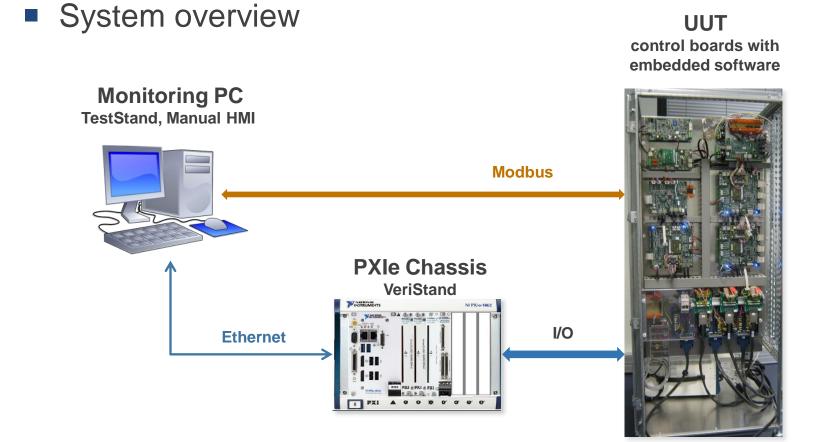

- Partnership between 2 leaders: NI and Opal-RT

- The solution:

- Opal-RT eHSx64 solver for NI FPGA boards

- NI VeriStand for the hardware interface and models

- NI TestStand for the test sequence automation

- NI LabVIEW programming language used for:

- VeriStand Slow Models and Custom Devices

- TestStand Custom Steps and Operator Interface

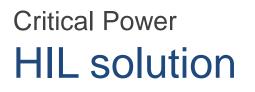

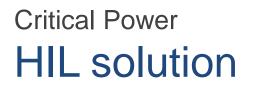

### Hardware solution:

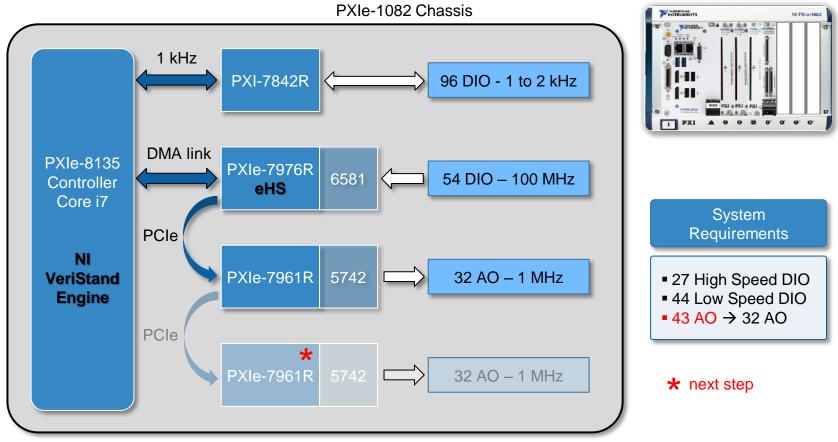

### Critical Power HIL simulation results

### Critical Power HIL simulation results

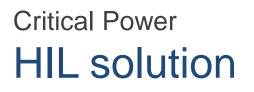

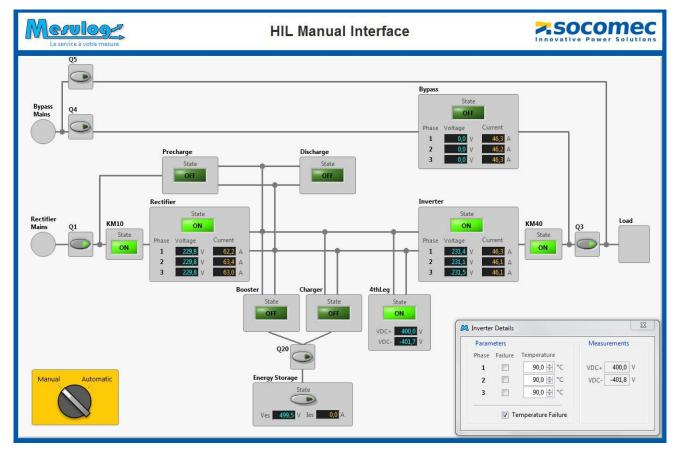

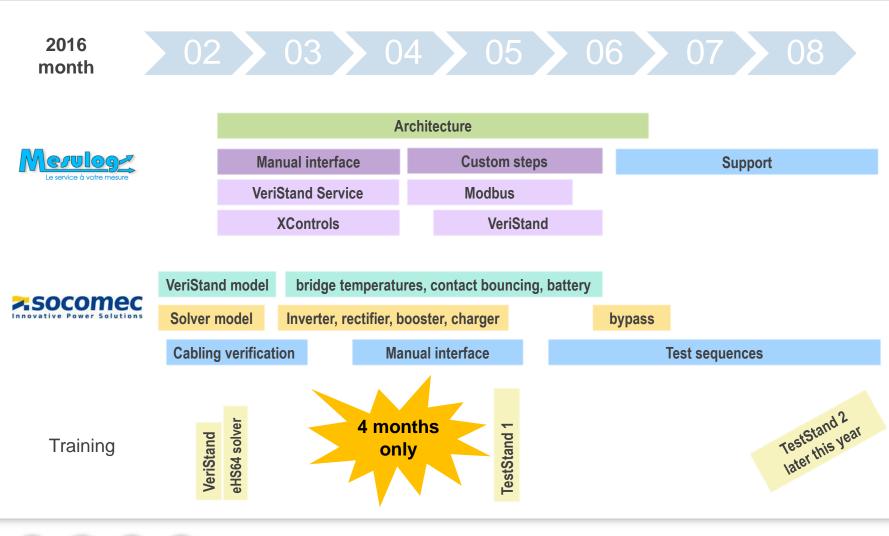

- Collaboration with MESULOG, NI partner

- Software architecture

- Manual HMI (Monkey Test)

- TestStand Step Types and Operator Interface

- Software development support and assistance

- Manual HMI (Monkey test)

- User-friendly interface for operators

- Developed with LabVIEW and VeriStand API

- VeriStand Workspace not used by operators

- Will be integrated later into TS Operator Interface

### Manual HMI (Monkey test)

### 27

- Manual HMI

- Innovative solution

- Modular and generic

- Power brick classes

- 11 XControls

- One per class

- 18 instances

- Linked to VeriStand alias sub-folder

- Continuous value update

- Additional pop-up panels

NIWeek Austin

August 2016

### TestStand Custom Step Types : PROTOCOL

- Abstraction layer to access

UUT internal data via Modbus

- Based on a XML file, that describes product data structure

- Configuration with a tree browser

- Search tool

- Based on TestStand add-on

www.mesulog.fr/modbussteps

| Item                   | Description            |          |

|------------------------|------------------------|----------|

| E C Product            | Description            | <u> </u> |

| GOMBoard               |                        |          |

| 🗏 🏬 Comboard           |                        |          |

| Areasurements          |                        |          |

| 123 AMInvVmM000        | Output Load Rate       |          |

| 123 AMInvVmM001        | Output Load Rate L1    |          |

| 123 AMInvVmM002        | Output Load Rate L2    |          |

| 123 AMInvVmM003        | Output Load Rate L3    |          |

| 123 AMInvVmM004        | Output Apparent Power  |          |

| 123 AMInvVmM005        | Output Active Power    |          |

| 123 AMInvVmM006        | Output current L1      |          |

| 123 AMIn√VmM007        | Output current L2      |          |

| 123 AMInvVmM008        | Output current L3      |          |

| 123 AMInvVmM009        | Output Neutral current |          |

| 123 AMInvVmM010        | Output voltage L1      |          |

| 123 AMInvVmM011        | Output voltage L2      |          |

| 123 AMInvVmM012        | Output voltage L3      | -        |

| D M MT or M (mon M 012 | Output frequency       |          |

| Acronym: AMInvVmM001   |                        |          |

|                        |                        |          |

|                        |                        |          |

28

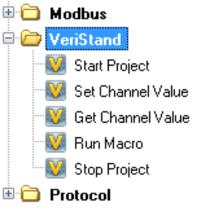

- TestStand Custom Step Types : VeriStand

- Modular and reusable steps to interact with VeriStand

- TestStand Custom Step Types : UTILITIES

- Specific SequenceCall with retry strategy on expected errors

### Critical Power HIL schedule

NIWeek Austin August 2016

### Critical Power HIL results

- Feedbacks

- What doesn't work on the HIL, will not work on the prototype

- Once a problem detected, it is easy to reproduce and replay

- A problem is solved in a shorter time (about a third / physical prototype)

- Main firmware problems already detected

- Specification interpretation

- Timing

- Signal filtering

- Closed loop control stability

- HIL few human bugs <sup>(2)</sup>

- Physical cabling (wrong input/output, signal inversion)

- LabVIEW models development

- Wrong sensor gain settings (400V signals to 0-5V signals adaptation, current sensors)

- Test sequence timing compare to UPS internal variable settling time

- Next steps

- Higher power systems

- more IGBT switches to control

- Parallel systems

- At least 2 units in parallel with same I/O latency

- Target : 16 units in parallel (16 x 150 IOs = 2400 IOs)

- Opal-RT solver improvement

- next NI FlexRIO board ?

# thank you SO much!

### Contacts :

- SOCOMEC : thierry.rohmer@socomec.com

- NAT. INSTR. : christophe.soares@ni.com ben.black@ni.com

- MESULOG : jls@mesulog.fr